วิธีสร้างตัวส่งสัญญาณ UART แบบอนุกรมอย่างง่ายใน verilog HDL

Universal Asynchronous Receiver Transmitter (UART) ส่วนใหญ่ที่ฉันพบทางออนไลน์ ซับซ้อนเกินไปและเข้าใจยาก ในที่นี้ ฉันจะอธิบายทฤษฎีง่ายๆ และโค้ดเกี่ยวกับวิธีสร้าง

ก่อนอื่นเรามาพูดถึงวิธีการทำงานของเครื่องส่งสัญญาณกันก่อน หลักการพื้นฐานคือการส่งข้อมูลหลายบิตในบรรทัดเดียว ในเครื่องส่งของเรา ข้อมูลนี้เป็นแบบขนาน อย่างไรก็ตาม เพื่อลดจำนวนสายที่ต้องการ เราใช้การสื่อสารแบบอนุกรมที่แปลงเป็นแบบขนานที่ปลายทางรับ

สิ่งพื้นฐานที่เราต้องการมีดังต่อไปนี้:

- ตัวแบ่งนาฬิกา (เคาน์เตอร์ของเรา)

สิ่งนี้ทำให้เราสามารถส่งข้อมูลด้วยความเร็วที่แน่นอน (อัตราบอด) ผู้รับของเราจะสุ่มตัวอย่างและรับข้อมูลทีละบิต

- ทะเบียนกะ

เราจำเป็นต้องทราบจำนวนบิตที่เราส่งในแต่ละครั้ง shift register ของเราจะมีบิตเริ่มต้น บิตข้อมูล บิตพาริตี (ตัวเลือก) บิตสิ้นสุด

- แผนภาพสถานะ

ก่อนเขียนโค้ดใด ๆ เราต้องคิดถึงสิ่งที่เราต้องสร้างและวิธีที่ดีที่สุดคือการสร้างไดอะแกรมสถานะของการออกแบบของเรา เราทราบดีว่าเครื่องส่งสัญญาณต้องมี 2 สถานะ คือ ไม่ได้ใช้งานและกำลังส่ง

หลังจากมีแผนภาพสถานะแล้ว เราก็สามารถคำนวณได้ว่าตัวนับของเราจะเป็นเท่าใด ทำได้โดยใช้:

ตัวนับ = ความเร็วสัญญาณนาฬิกา FPGA/ อัตราบอด

ในตัวอย่างนี้ ฉันใช้อัตราบอดที่ 9600 ทำให้ตัวนับของฉัน = 5208

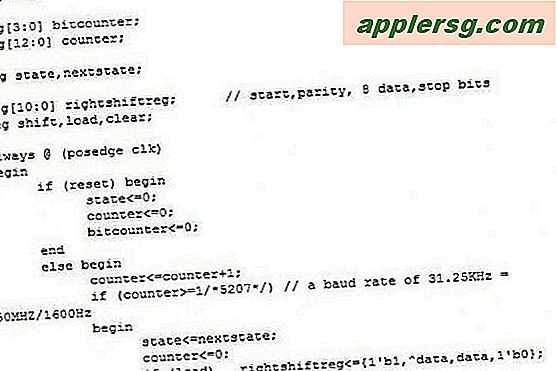

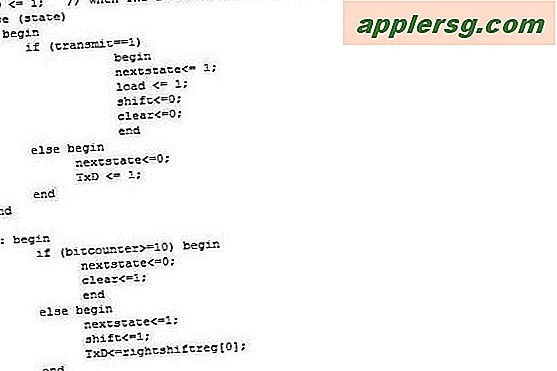

สุดท้าย เราคำนวณ shift register และเขียน state machine ให้เสร็จ ในโค้ดตัวอย่างของฉัน ฉันใช้บิตเริ่มต้น, พาริตีบิต, ข้อมูล 8 บิต และบิตสิ้นสุด รวมเป็น 11 บิต

รูปภาพทั้งสองในขั้นตอนที่ 2 และ 3 ร่วมกันในโมดูลเดียวกันจะกรอกรหัสเครื่องส่งสัญญาณที่จำเป็นในการเขียนโปรแกรมไปยัง FPGA รหัสนี้จะทำงานกับ FPGA อื่นที่เชื่อมต่อแบบอนุกรมหรือกับ windows hyperterminal ร่วมกับฮาร์ดแวร์อื่นๆ สามารถปรับเปลี่ยนการทำงานได้ง่ายมากยิ่งขึ้นอีกด้วย

สุดท้าย เราสร้างชุดทดสอบเพื่อแก้ไขข้อผิดพลาดและจำลองโปรแกรมของเราก่อนที่จะตั้งโปรแกรม FPGA

นี้สรุปเครื่องส่งสัญญาณ โปรดแสดงความคิดเห็นหากคุณมีคำถามหรือรู้สึกว่ามีบางอย่างขาดหายไปที่นี่

เคล็ดลับ

ทั้งตัวส่งและตัวรับต้องทราบอัตราบอดที่ข้อมูลกำลังถูกส่ง